One of my smart (Zigbee) LED bulbs started flickering, then gradually lost brightness over several weeks, and finally went completely dark.It was an OSRAM SMART+ AC03641 2700k 810lm 8.5 Watt I bought a new one (actually, I bought two new LED bulbs because this type Read More …

Reviving a USB power sensor Mini-Circuits PWR-SEN-6G+, Part IX: Temperature

The RF power sensor contains a temperature sensor for compensating the temperature dependence of the diode forward voltage and leakage current and maybe also some other, minor effects like the temperature coefficient of the reference voltage source and the temperature dependency of the input current Read More …

Reviving a USB power sensor Mini-Circuits PWR-SEN-6G+, Part VIII: U vs. level, frequency

From the original GUI I know that the RF power sensor requires to input the measurement frequency with a resolution of 1 MHz. This is the reason why I decided to scan my SMY02 from 1 MHz up to its highest output frequency of 2080 Read More …

Reviving a USB power sensor Mini-Circuits PWR-SEN-6G+, Part VII: How to calibrate?

I do not have an RF power calibration source and I do not know where to borrow one.What I have available is a used Rohde & Schwarz SMY02 signal generator, which I bought second-hand a few years ago and which has a calibration sticker from Read More …

Reviving a USB power sensor Mini-Circuits PWR-SEN-6G+, Part VI: Micropython Drivers

The ADC AD7791 is the most important part of the RF power sensor – apart from the diode detector. It has to convert the output voltage of the diode detector accurately and with very low fluctuations into digital values.At low input powers, the input voltages Read More …

Reviving a USB power sensor Mini-Circuits PWR-SEN-6G+, Part V: 3.3V-5V

The old MCU ran directly from the USB Bus voltage, namely ~4.75…5V.All the peripherals had to be connected to the same voltage, because this was also the I/O voltage of the MCU. Now the situation is different: The Raspberry Pico runs on 3.3V and has Read More …

Reviving a USB power sensor Mini-Circuits PWR-SEN-6G+, Part IV: cable problems

I couldn’t believe it at first, but the manufacturer’s original USB cable is unshielded.This could explain the USB error when connecting the PICO.How can I change this?I really wanted to keep the nice LEMO connector!Fortunately, the LEMO connector is shielded. So how about using a Read More …

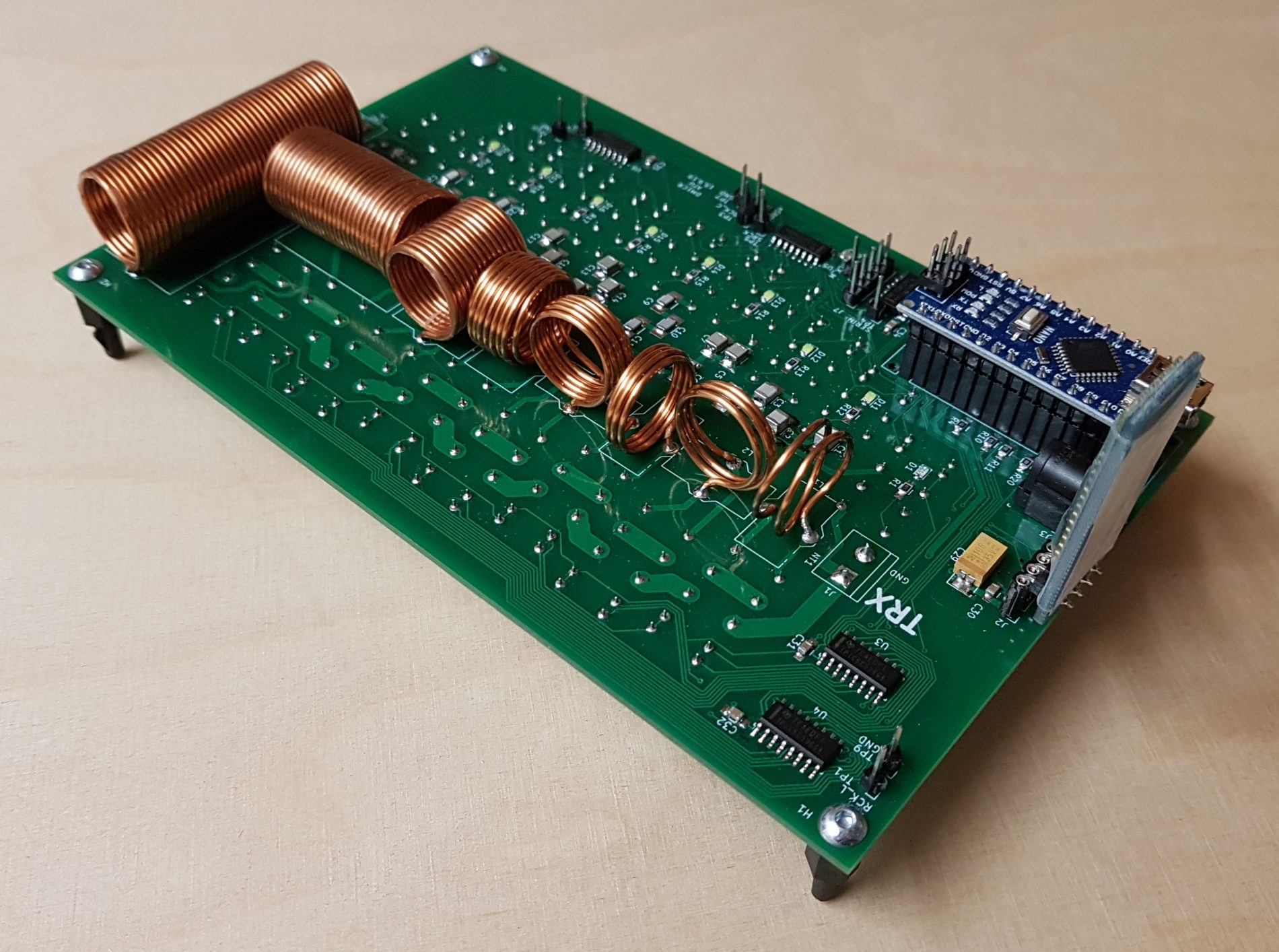

Reviving a USB power sensor Mini-Circuits PWR-SEN-6G+, Part III: Pico to the rescue?

The CYC7C64743 microcontroller is outdated. There’s no USB driver for Windows 10 or Windows 11. It’s probably best to remove this part and replace it with something else. The RF power sensor uses essentially an ADC with an SPI interface for reading the DC voltage Read More …

Reviving a USB power sensor Mini-Circuits PWR-SEN-6G+, Part II: Detective Work

The integrated circuits are small, but all have markings that can be clearly seen with the help of a magnifying glass: CY7C63743: The CY7C63743 is a „enCoRe™ USB Combination Low-Speed USB and PS/2 Peripheral Controller“ The part is obsolete, but its datasheet can still be Read More …

Reviving a USB power sensor Mini-Circuits PWR-SEN-6G+, Part I: Teardown

This new blog entry is about a USB RF power sensor. I haven’t had much time for leisure projects in recent years, but in this case, I thought it would be a small project I could manage. Of course, it turned out to be much Read More …